JPEG 2000 由 intoPIX

intoPIX的艾美獎®獲獎 JPEG 2000 IP-內核 保護高價值映射。同時處理深色、高數據速率和廣泛的 JPEG2000 專有技術, IP-內核可實現一流的畫質。

可用於最新的平台和工藝節點, intoPIX IP-內核使其用戶能夠在比特率、幀速率、解析度、功耗和可擴充性方面實現前所未有的性能。

受益於模組化架構,並配有各種外圍設備和安全性 IP-核心 intoPIX的解決方案提供了一種簡單、及時且經濟高效的方式來實施 JPEG 2000年獨一無二的技術 intoPIX 附加值

超低延遲模式

獨一無二 intoPIX

超低延遲模式(子 I 幀)編碼在編碼時低至幀(場)的 2/16,在解碼時低至 1/16 幀(場),並具有條帶邊界保護。

(例如,在 1080p60 或 2160p60 中進行端到端壓縮時,低至 5 毫秒)

主要特點

瞭解我們的 JPEG 2000 IP 核心

intoPIX 提供廣泛的 JPEG2000 編碼器/解碼器 IP-針對各種應用優化的內核。基於我們支援的所有 功能,可以提供自定義版本以滿足您的特定需求。

聯繫我們,根據您選擇的進行自己的配置 FPGA 平臺或 ASIC 以及以下典型設定清單:

特徵

| 圖像/視頻功能 |

|

| JPEG 2000 壓縮 (ISO 15444-1 及更多) |

|

| 品質和比特率控制 |

|

| 延遲 |

|

| 控制 |

|

| FPGA/ASIC |

|

* 如果您希望避免任何 DDR 要求, intoPIX 提供其他壓縮 IP-無需任何外部記憶體的內核: TICO XS(JPEG XS), TICO RDD35 或 TICO-RAW (感測器壓縮)

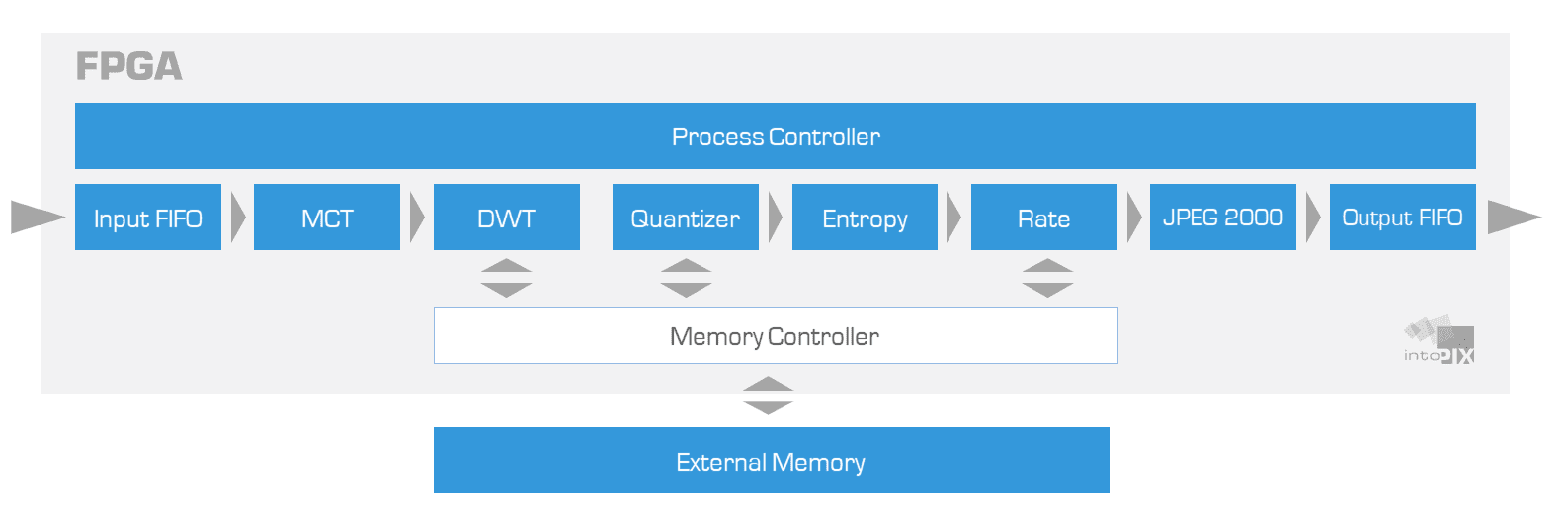

編碼器架構

點擊圖片放大

編碼器的第一階段是多分量變換,它可用於提高壓縮效率,通過從色度中去除亮度,例如將RGB轉換為YCbCr。可以使用3種模式:直通,可逆無損變換(RCT,規定用於無損編碼))和不可逆變換(ICT)。RCT和ICT轉換均以18位定點精度實現。

離散小波變換 (DWT)

子帶的二維小波分解使用勒加爾(5/3)濾波器組或多貝西(9/7)濾波器組進行。建議使用 5/3 濾波器進行無損編碼,而 9/7 濾波器為有損編碼提供更好的壓縮效率。以18位定點精度使用。

量化

小波子帶的係數被量化。量化步驟由用戶定義,每個子頻段可以不同。

熵編碼器

每個小波子帶被分成幾個代碼塊,並使用熵編碼器進行編碼。編碼器分為兩個塊:上下文建模器和算術編碼器。上下文建模器通過將描述每個位鄰域的信息發送到算術編碼器,連續對代碼塊的每個位平面進行編碼。利用這些資訊,算術編碼器對每個位進行編碼,以生成壓縮的比特流。

費率分配器

JPEG 2000發電機

這 JPEG 2000 生成器負責生成最終的代碼流,以便提供完全相容的代碼流 JPEG 2000年圖像。該代碼流生成器還根據用戶選擇的可伸縮性順序負責代碼流結構:按解析度 (R)、按品質層 (L)、按位置 (P) 或按元件 (C)。

外部記憶體

介面

輸入和輸出介面基於 FIFO 協定,輸入介面需要兩個像素的突發(RBG、XYZ 或 YUV)。

過程控制器

充分利用 JPEG 2000幀內編碼, intoPIX 編碼器過程式控制器精確管理幀流。當沒有視頻編碼時,處理器將繼續提供最新的編碼幀,或者停止根據使用者命令輸出壓縮數據。此過程還配置不同的 JPEG 完整編碼鏈的 2000 個選項。

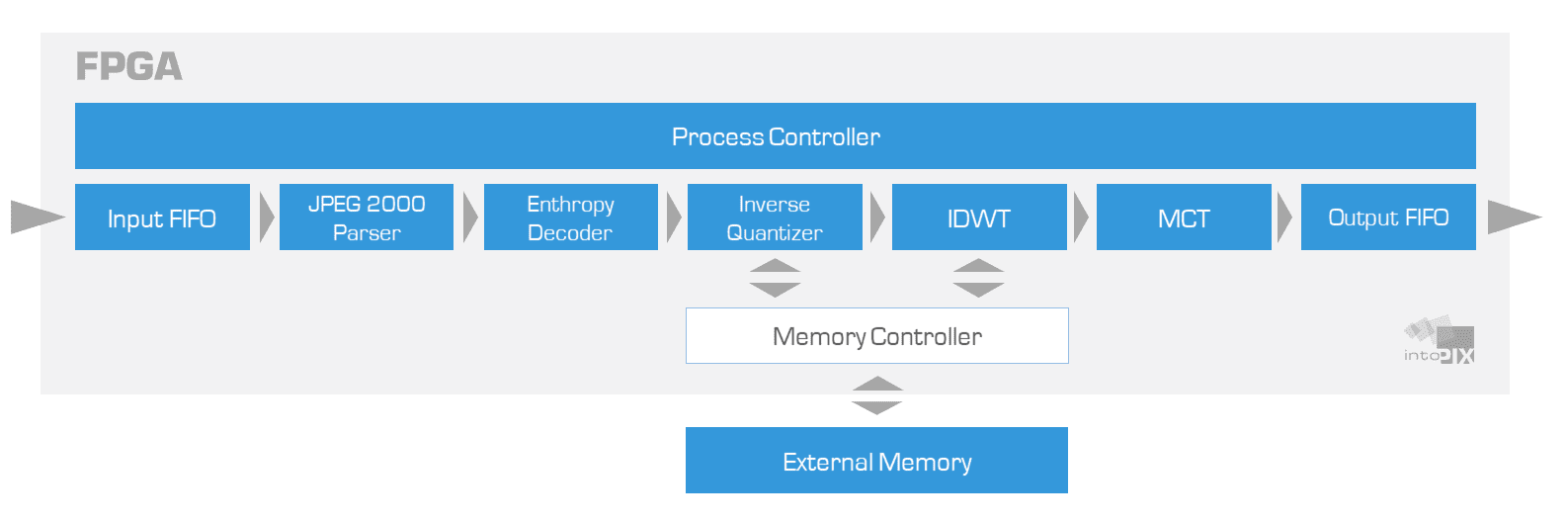

解碼器架構

點擊圖片放大

JPEG 2000 解析器

這 JPEG 2000 解析器分析了 JPEG 2000 碼流並將壓縮的比特流發送到熵解碼器。

熵解碼器

每個小波子帶分為幾個代碼塊的重建由兩個模組實現:上下文建模器和算術解碼器。上下文建模器通過將描述每個位鄰域的信息發送到算術解碼器,連續解碼代碼塊的每個位平面。利用這些資訊,算術解碼器對位流進行解碼。

逆量化器

小波子帶的係數是逆量化的。量化步驟在 JPEG 2000 檔,每個子帶可以不同。

外部記憶體

幀記憶體緩衝器用於逆量化器輸出,可實現高效的IDWT處理。該緩衝區包含一個 DDR-SDRAM 外部記憶體,始終保留至少一個有效幀,可以在方便時重複。

逆離散小波變換 (IDWT)

實現了子帶的二維小波重構。可以使用兩個具有 18 位定點精度的濾波器組:用於無損編碼的 Le Gall (5/3) 濾波器組或用於有損編碼的更複雜的 Daubechies (9/7) 濾波器組。

多組分轉換 (MCT)

在 JPEG 2000標準,為了提高壓縮效率,可以採用多組分變換。根據所使用的小波濾波器,定義不同的變換。可逆變換(RCT)與5/3濾波器一起使用,不可逆變換(ICT)與9/7濾波器一起使用。兩種轉換均以18位定點精度實現。

錯誤處理

解碼器旨在檢測輸入數據中的錯誤,並在主標頭和

標籤樹的一致性。檢測到錯誤時,會將特定錯誤代碼發送到管理解碼器的設備。在幀代碼流損壞的情況下,解碼器可以嘗試解碼下一幀。可以重複此操作,直到遇到正確的幀。如果在幀速率確定的經過時間內無法解碼任何幀,則會將先前正確解碼的幀發送到輸出以防止顯示偽影。

過程控制

利用 JPEG 2000幀內編碼,解碼器控制器可以以幀精度(或以下的超低延遲模式)管理流。當輸入端沒有要解碼的數據時,解碼器可以迴圈訪問最新的解碼幀,輸出黑幀或停止輸出幀。通過控制輸入流和輸出選項,解碼器控制器可以管理暫停、逐步、慢動作、快進和快退以及隨機訪問。

介面 輸入通過小端或大端表示的 32 位突發接收數據。輸出兩個像素(RGB、XYZ 或 YUV)的突發。輸出時鐘取決於序列幀速率和圖像大小。

阿德-Xilinx FPGA 和 SoC IP

從斯巴達到阿蒂克斯、金特克斯、Zynq、維爾泰克斯家族

ASIC 智慧財產權

告訴我們更多關於您的需求

Intel-阿爾特拉 FPGA & SoC IP

從旋風到Arria&Stratix家族

我們的用戶怎麼說

索尼數位影院

北澤敏彥,DC部高級技術經理

奧丁 - 但丁AV

“這種新產品的好處之一是能夠通過1Gigabit網络傳輸所有東西。這是我們使用的壓縮的結果。來自的編解碼器 intoPIX 使我們能夠無縫地做到這一點,而且具有高品質和4K清晰度。

Lee Ellison, 首席執行官

阿特爾視頻系統

“在開發我們的解決方案時,我們選擇了 intoPIX 核心,因為它已迅速成為行業標準。

理查·德拉卡諾尼卡,總裁

快思聰

"intoPIX的 JPEG 2000 超低延遲技術是 DigitalMedia NVX 系列傳輸 4K60 4:4:4 HDR 視頻不可或缺的一部分,具有標準 1 Gb 乙太網網路的全部功能,並且沒有延遲。它代表了高性能視頻傳輸的巨大飛躍 IP 網路。

史蒂夫·薩姆森,業務發展執行總監

媒體連結

NEC 顯示解決方案

“我們選擇了 intoPIX 因為他們在 JPEG 2000年壓縮技術領域,其智慧單晶元 FPGA 實施及其集成支援。

黑田敦, 總經理

內維翁

“我們選擇了 intoPIX JPEG VS902平臺的2000技術基於其性能,互操作性和完全符合最新技術標準,如 JPEG2000 廣播配置檔。此外,他們在以下方面的專業支持和專業知識 JPEG 2000 技術使我們能夠為客戶開發高度定製的解決方案。

許振哲博士,P·羅duct 管理人

NTT AT

"intoPIX JPEG 2000種高品質編解碼器完美地解決了為視聽行業提供更多圖元和更高幀速率的挑戰。跟 JPEG2000,所有格式的視頻質量始終保持卓越。它是逐幀壓縮,解析度可擴展,它以視覺甚至數學無損的方式壓縮圖片,延遲非常低。

高梨仁, 營業單位經理

相關IP和 SDKs

- JPEG 2000 高清編碼器/解碼器 IP-核心 FPGA & ASIC

- JPEG 2000數位影院編碼器/解碼器 IP-核心 FPGA & ASIC

- JPEG 2000 UHDTV 4K/8K 編碼器/解碼器 IP-核心 FPGA & ASIC

- JPEG 2000 數學無損(高達16位)編碼器/解碼器 IP-核心 FPGA & ASIC

- 多埠 DDR 記憶體控制器 IP-核心 FPGA 最適合 JPEG2000 編碼器/解碼器 IP 和其他IP

- MPEG2-TS 封裝/解封 IP-核心 JPEG2000 VSF TR01(版本 1 和版本 2)

- 加密/加密(AES,RSA,HMAC-SHA1,水印介面) FPGA IP-核心